HLCCAD System for Blended Learning of Digital Electronics Basics

HLCCAD System for Blended Learning of Digital Electronics Basics

Abstract

The article describes a practical experience of blended learning based on the application of DL.GSU.BY (DL) distance learning tool system and HLCCAD system, which provides design, modelling and analysis of functional circuits of digital systems and integration with DL for automatic verification of circuits of digital devices developed by students. Both software products were developed at the Francisk Skorina Gomel State University under the author's supervision. DL provides student access to theory and design and analysis tasks, as well as sending solution files for both types of problems. HLCCAD provides visual development and debugging by students of functional schemes of digital devices, as well as checking the correctness of the schemes sent by students for verification by their simulation on a set of tests specified by the author of the task. HLCCAD also provides verification of tasks for analysis of functional circuits of digital devices by simulation of tests sent by the student on the author's solution.

1. Введение

Автор более четверти века преподаёт основы цифровой электроники студентам первого/второго курсов факультета математики и технологий программирования Гомельского государственного университета им. Ф. Скорины. Данная учебная дисциплина является очень важной как для изучения последующих дисциплин данного направления, таких как «Архитектура вычислительных систем», «Проектирование программно-аппаратных средств», «Встроенные системы», так и для закладывания фундаментальных знаний об устройстве и алгоритмах функционирования вычислительных систем для обеспечения качественного изучения всех последующих дисциплин по языкам, системам и технологиям программирования. Интенсивное развитие вычислительной техники и средств разработки аппаратного и программного обеспечения приводит к необходимости наполнения учебной дисциплины всё новыми и новыми учебными материалами, в то время как учебные часы, отведённые на её изучение, остаются практически неизменными. Естественным ответом возникающим вызовам является развитие новых методов и средств обучения, в том числе и прежде всего, основанных на применении новых информационных технологий. Смешанное обучение , предполагает интеграцию традиционных подходов с онлайн обучением, максимально используя как возможности преподавателя в аудитории, так и средства современных информационных технологий в аудитории и при самостоятельной работе студентов. В частности, в аудиторных занятиях преподаватель может кратко изложить теорию и объяснить какие программные средства могут использовать студенты при работе в учебных классах и самостоятельной работе. Кроме того, часть учебного времени впоследствии может быть использована для ответов на вопросы и индивидуальных консультаций. Основная часть учебного времени как в учебных аудиториях, так и при самостоятельной работе дома, должна быть посвящена взаимодействию с предложенными учебными материалами и программными системами, берущими на себя значительную часть традиционной работы преподавателя по изложению теории, выдаче практических заданий, помощи в процессе их выполнения, контролю за правильностью выполнения и итоговому оцениванию работы студента в течение семестра.

В работах , , , описываются примеры успешного использования смешанного обучения в университетском образовании по самым различным специальностям. В работе представлен авторский опыт смешанного обучения первокурсников основам программирования. В работе представлен авторский опыт смешанного обучения студентов младших курсов основам цифровой электроники. Основные отличительные особенности авторского подхода таковы:

1. Использование сайта дистанционного обучения DL.GSU.BY, разрабатываемого с 1999 года под руководством автора, обеспечивающее

· перманентную интеграцию теории по предмету, включая опорные конспекты лекций используемые совместно с мультимедийной аппаратурой

· форум для интерактивного взаимодействия в течение семестра студентов с преподавателем и систематического тематического накопления вопросов студентов и ответов преподавателя, используемых в обучении следующих поколений студентов

· систему обеспеченных автоматической проверкой контрольных вопросов и практических заданий по темам лекций. При этом практические здания используются как во время лекционных занятий для оперативного контроля усваивания теории и активизации познавательной деятельности студентов во время изучения теории; так и при самостоятельной работе студентов в учебных классах и дома по закреплению изученной теории; а также при контрольной проверке знаний, умений и навыков полученных студентами.

2. Использование системы HLCCAD (High Level Chip Computer Aided Design), разрабатываемой с 1997 года под руководством автора для визуального проектирования цифровых устройств, их симуляции и отладки. Визуализация, симуляция и отладка сильно повышают качество усваивания учебного материала, а интеграция систем HLCCAD и DL.GSU.BY выводит на новый уровень автоматизацию проверки соответствующей учебной работы студентов.

Данная статья посвящена подробному изложению использования системы HLCCAD при обучении студентов основам цифровой электроники. Приводятся виды заданий, которые предлагаются к выполнению студентами, а также описываются возможности системы HLCCAD, позволяющие студентам успешно справляться с предлагаемыми заданиями.

2. Формулирование проблемы

Основы цифровой электроники – новый и сложный для изучения предмет для студентов младших курсов, с которым большинство из них сталкивается впервые. Дополнительные проблемы создают существенные различающиеся у разных студентов умения учиться и мотивация. Вместе эти факторы ставят перед преподавателем сложную задачу по обучению.

Для того чтобы конкретизировать содержание предмета и подтвердить новизну материала для большинства студентов, далее приводится первый раздел теории, которая подлежит изучению.

Логические элементы и логические операции

Отрицание, конъюнкция, дизъюнкция. Сложение по модулю 2. Основные тождества. Переход от логических функций к схемам. Среда проектирования и моделирования цифровых устройств HLCCAD. Базовые понятия: проект, устройство, корпус, схема, контакт, библиотека стандартных устройств.

Минимизация булевых функций

Понятие о таблицах истинности. Построение таблиц истинности для функциональных устройств без памяти. Минимизация логических функций методом карт Карно. Расстановка единичных значений. Покрытие карт. Логические функции покрытия. Примеры решения задач.

Комбинационные схемы

Дешифратор. Условное графическое обозначение. Таблица истинности. Логические функции. Выдача логического сигнала “1” по той выходной линии, двоичный код которой стоит на входных линиях.

Шифратор. Условное графическое обозначение. Таблица истинности. Логические функции. Получение номера входной линии, на которой находится логический сигнал “1”.

Приоритетный шифратор. Условное графическое обозначение. Таблица истинности. Логические функции. Получение номера верхней входной линии, на которой находится логический сигнал “1”.

Мультиплексор. Условное графическое обозначение. Таблица истинности. Логические функции. Передача на выход значений входной линии, номер которой стоит на адресном входе. Шинный мультиплексор.

Сумматор. Условное графическое обозначение. Таблица истинности. Логические функции. Двоичное сложение многоразрядных данных. Входной и выходной переносы.

Запоминающие устройства

Триггер. Условное графическое обозначение. Таблица истинности. Логические функции. Понятие о бите. Статический D-триггер. Динамический D-триггер по переднему фронту. Динамический D-триггер по заднему фронту. Временные диаграммы. Режим загрузки. Режим хранения.

Регистр. Условное графическое обозначение. Таблица истинности. Логические функции. Статический регистр. Динамический регистр по переднему фронту. Динамический регистр по заднему фронту. Временные диаграммы. Режим загрузки. Режим хранения. Режим сброса. Синхронное и асинхронное управление регистром.

Счетчик. Условное графическое обозначение. Таблица истинности. Логические функции. Временные диаграммы. Режим загрузки. Режим хранения. Режим сброса. Режим прямого счета. Режим обратного счета. Синхронное и асинхронное управление счетчиком.

Оперативное запоминающее устройство. Условное графическое обозначение. Таблица истинности. Логические функции. Двумерная матрица памяти. Режим записи. Режим чтения. Режим хранения. Зависимость емкости ОЗУ от разрядности входных и адресных линий. Понятие о третьем состоянии (Z-состоянии).

Постоянное запоминающее устройство. Условное графическое обозначение. Таблица истинности. Логические функции. Двумерная матрица памяти. Запись в процессе изготовления. Режим чтения. Режим хранения. Зависимость емкости ОЗУ от разрядности входных и адресных линий. Использование Z-состояния в постоянных запоминающих устройствах.

3. Решение проблемы

3.1. Идеология изучения основ цифровой электроники с помощью HLCCAD

Для решения обозначенной выше проблемы проводится смешанное обучение с помощью системы дистанционного обучения DL.GSU.BY, в которую погружены необходимая теория и практические задания на проектирование и анализ схем цифровой электроники. Выполнение студентами заданий и проверка решений осуществляется с помощью системы HLCCAD. HLCCAD обеспечивает графический ввод и редактирование схем цифровой электроники, моделирование и отладку с помощью визуализации результатов моделирования, а также генерацию VHDL-описания при необходимости создать реальное устройство, например с помощью FPGA.

Таким образом, закрепление теории и проверка её изучения осуществляется с помощью выполнения автоматически проверяемых заданий на проектирование и анализ соответствующих функциональных схем цифровой электроники.

3.2. Примеры заданий на проектирование схем

Изучение теории основ цифровой электроники закрепляется решением задач на проектирование и анализ цифровых схем следующих видов

- по логической функции

- по таблице истинности

- комбинационная схема

- условное арифметическое выражение

- схема с памятью

Проверка правильности выполнения задания осуществляется следующим образом. На стороне клиента отправляется файл схемы. На стороне сервера запускается система HLCCAD с этой схемой и подготовленными автором тестами (входными воздействиями и правильными ответами для этих воздействий). Производится автоматическая сверка ответов, полученных в результате моделирования решения студента на заданных входных воздействиях, и ответов автора. В случае совпадения всех ответов за всё время моделирования, решение принимается, иначе – нет, и студенту сообщается, для каких входных воздействий схема студента неправильно просчитала значения на выходах.

Задача П1. Проектирование по логической функции. Построить цифровое устройство, удовлетворяющее следующей булевой функции: OUT_0=((IN_0+IN_1) V ~IN_2) V (IN_3+IN_4) на входе которого однобитные числа IN_0, IN_1, IN_2, IN_3, IN_4, а на выходе OUT_0 (однобитное).

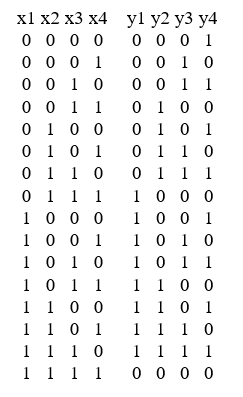

Таблица истинности

входные переменные x1 x2 x3 x4, выходные переменные y1 y2 y3 y4

Условное арифметическое выражение

3.3. Примеры заданий на анализ функциональных схем цифрового устройства

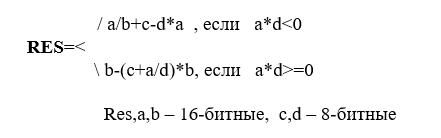

Во всех заданиях на анализ функциональной схемы цифрового устройства студенту предъявляется её рисунок, на входные контакты подаются случайные значения (они отображаются на рисунке). Студент должен понять схему и просчитать значения на выходах для данных входных. Значения на выходах меняются с 0 на 1 и обратно кликами по соответствующей цифре. Входные воздействия подаются 10 раз и студент должен столько же раз правильно изменить выходные значения. Проверка правильности выполнения задания осуществляется следующим образом. На стороне клиента формируется файл тестов из случайных поданных входных воздействий и ответов студента и этот файл отправляется на сервер. На стороне сервера запускается система HLCCCAD с авторским решением этой задачи (которое предъявлялось на рисунке задания) и принятым от клиента тестовым файлом. Производится автоматическая сверка ответов, полученных в результате моделирования авторского решения на заданных входных воздействиях и ответов студента. В случае совпадения всех ответов за всё время моделирования, решение принимается иначе – нет, и студенту сообщается, для каких входных воздействий студент неправильно просчитал значения на выходах.

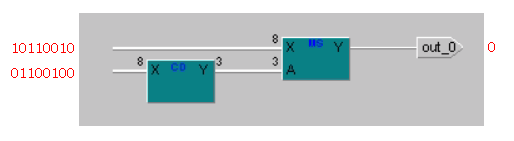

Задача А1. Анализ схемы из логических функций

Задача А2. Анализ комбинационной схемы

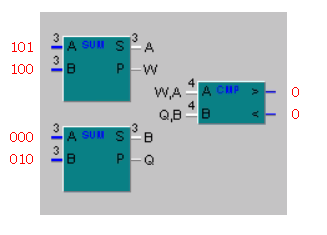

Задача А3. Анализ арифметической схемы

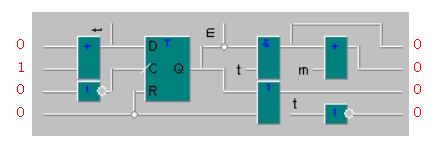

Задача А4. Анализ схемы с памятью

Система HLCCAD позволяет создавать устройства как «снизу-вверх», так и «сверху-вниз». Для создания нового проекта необходимо выбрать пункт меню главного окна «Файл|Новый проект». После указания имени файла, новый проект будет добавлен в окно «Инспектора проектов». Для того чтобы создать новое устройство, нужно вызвать локальное меню над именем проекта и выбрать пункт «Новое устройство», указав в диалоговом окне его имя.

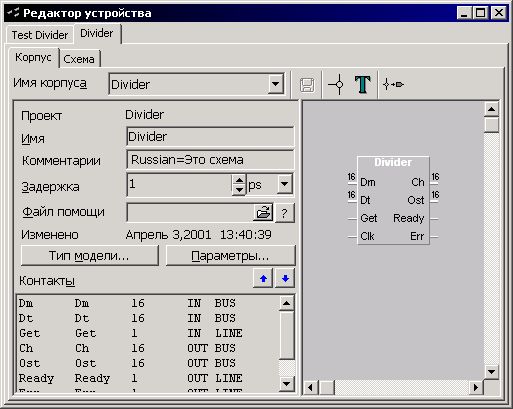

После этого разработчик может модифицировать корпус и схему устройства. Для открытия редактора необходимо вызвать локальное меню над именем устройства и выбрать пункт «Редактор».

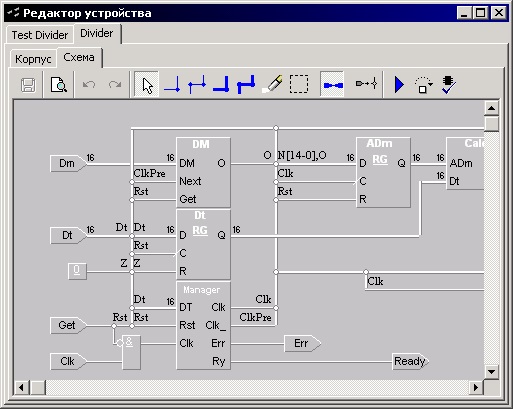

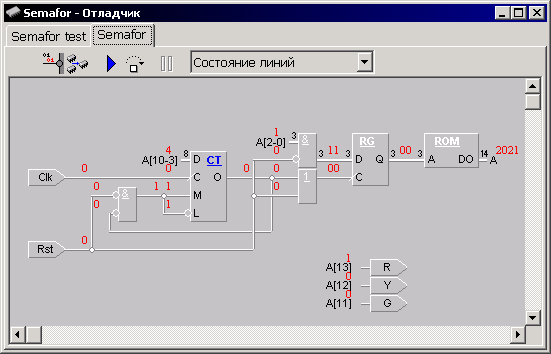

Окно редактора устройства состоит из двух подредакторов: редактор УГО (условное графическое обозначение) корпуса (рис. 7) и редактор схемы (рис. 8).

Редактирование корпуса устройства

Окно редактора схемы

Изменение УГО корпусов устройств после добавления на схему также осуществляется в окне редактора корпуса. Для этого в окне редактора предусмотрена возможность переключения редактируемого корпуса. После сохранения содержимого редактора, новое УГО корпуса автоматически обновляется на схеме.

Редактирование связей осуществляется 3 способами:

- рисование отдельных линий

- рисование ломаных

- использование невидимой шины

При рисовании линий разработчик определяет тип линии (одинарная или шина) путём нажатия соответствующей кнопки на панели. Рисование отдельных линий происходит по следующему алгоритму:

- нажать левую кнопку мыши на схеме

- переместить указатель мыши

- отпустить кнопку мыши

Рисование ломаных происходит так:

- щёлкнуть левой кнопкой мыши на схеме

- переместить указатель мыши.

- для рисования отрезка ломаной щелкнуть левой кнопкой мыши и повторять действия, выполняемые при рисовании линий

- для отмены кликнуть правую кнопку мыши.

При рисовании линий и шин допустимо использование невидимых (именованных) шин. Для ввода имени шины необходимо дважды щёлкнуть левой кнопкой мыши над линией и диалоговом окне ввести соответствующие названия.

Использование невидимой шины позволяет уменьшить число линий на схеме и тем самым сделать рисунок схемы более читабельным. Для ввода линий контакта в шину необходимо ввести имя, под которым эти линии будут доступны. Вызов окна ввода имени производится после двойного щелчка левой кнопкой мыши над контактом корпуса или схемы.

При разработке «снизу-вверх» предоставляется возможность объединять уже готовые устройства, устанавливая связи между ними.

3.5 Встроенная параметризированная библиотека стандартных устройств

Декомпозиция разрабатываемого устройства или его блока до получения симулируемых компонент осуществляется посредством создания схемы с использованием синтезируемых устройств. Таковыми являются устройства из базовой параметризированной библиотеки устройств «Standard.prd». В таблице 1 приведён список устройств, входящих в состав этой библиотеки. Разработчик может изменять добавлять или удалять контакты, изменять их параметры и разрядность в соответствии с функциональностью устройства. Высокоуровневая модель автоматически настраивается на алгоритм работы, соответствующий созданному условному графическому обозначению (УГО) корпуса и его параметрам.

Таблица 1 - Устройства библиотеки “Standard”

Логика | NOT | Логический инвертор |

OR | Логическое ИЛИ | |

XOR | Логическое исключающее ИЛИ | |

AND | Логическое И | |

Комбинационные схемы | CD | Приоритетный шифратор |

DC | Дешифратор | |

MS | Мультиплексор | |

DMS | Демультиплексор | |

Константы | 0 | Генератор логического «0» |

1 | Генератор логического «1» | |

BF | Тристабильный буфер | |

Память | T | Триггер |

RG | Регистр | |

CT | Счётчик | |

ROM | Постоянное запоминающее устройства | |

RAM | Оперативное запоминающее устройства | |

Математические операции | CMP | Компаратор |

SUM | Сумматор | |

MUL | Умножитель | |

DIV | Делитель |

3.6. Тестирование и отладка разработанных схем

Тестовые воздействия на моделируемое устройство можно подавать несколькими способами.

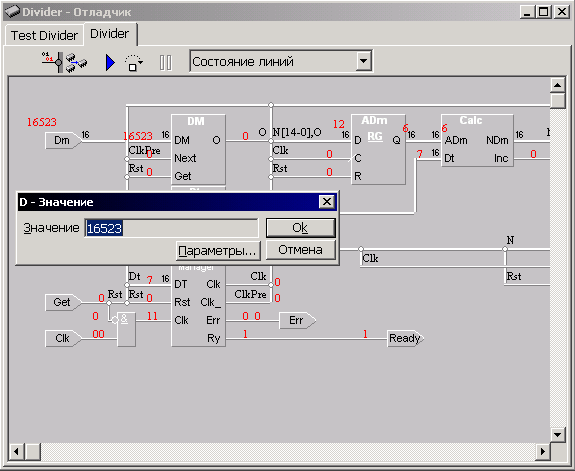

Во-первых, разработчик может интерактивно изменять значения на контактах. Для этого необходимо открыть соответствующее окно отладчика схем. Затем двойным щёлчком «мыши» вызвать окно изменения значения. После ввода нового значения достаточно нажать кнопку «Ok» (рис. 9).

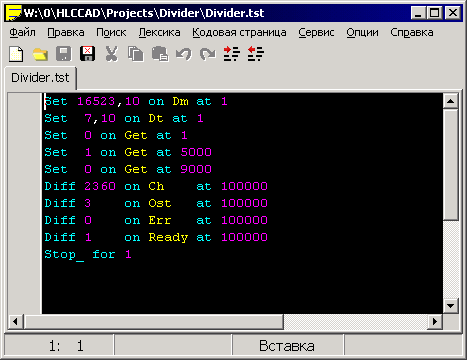

Во-вторых, реализован пакетный режим тестирования. Разработчик может указать набор тестовых воздействий в виде специализированного текстового файла (рис. 10). Для этого в окне редактора схемы нужно вызвать локальное меню и выбрать пункт «Параметры». В окне «Параметры схемы» необходимо указать соответствующее имя файла. Перед запуском на моделирование необходимо установить в параметрах моделирования флаг «Использовать тесты».

Пример интерактивного ввода

Пример файла тестовых воздействий

3.7. Визуализация результатов моделирования

Анализ результатов моделирования осуществляется при помощи широкого диапазона различных окон визуализации.

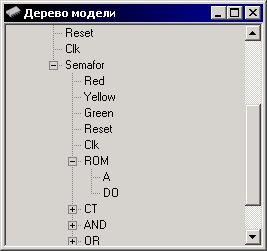

Дерево модели

Окно отладчика схемы

Окно навигатора по времени

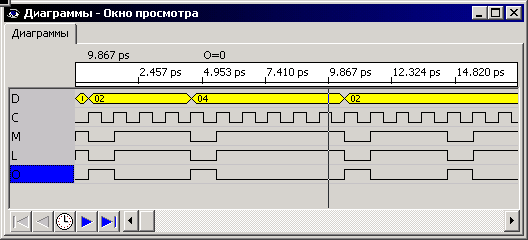

Окно временных диаграмм

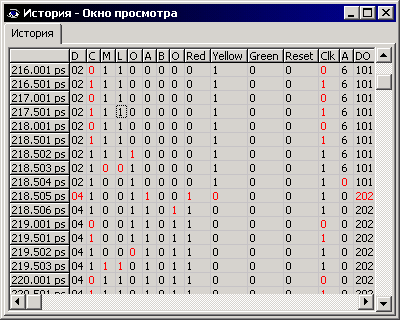

Окно истории контактов

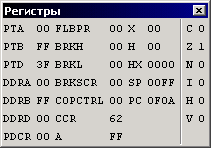

Окно просмотра регистров и флагов

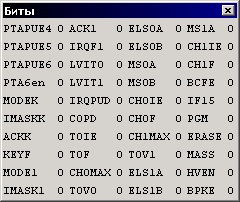

Окно просмотра битов

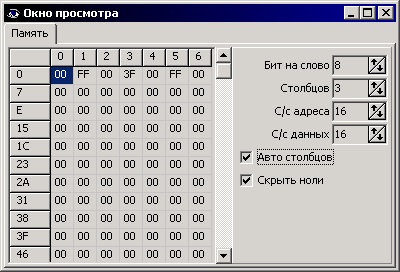

Окно просмотра дампа памяти (форматируемое)

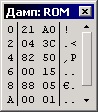

Окно просмотра дампа памяти (стандартное)

Для просмотра трассы значений для контактов предусмотрены два окна анализа: временных диаграмм и истории контактов. Окно временных диаграмм (рис. 14) является традиционным для систем разработки аппаратного цифрового обеспечения. В левой части отображаются имена контактов, а в правой – трасса значений в виде диаграммы. Имеются возможность масштабирования, фильтрации и поиска значения. Средства навигации аналогичны окну «навигатора времени». Окно истории контактов (рис. 15) отображает трассу значений в виде таблицы. Каждый столбец таблицы содержит значения контакта, в момент модельного времени, определённого строкой. Каждая строка таблицы всегда отличается от предыдущей, т.е. информация сжата.

Для анализа значений внутренних переменных моделей предназначено окно просмотра регистров и флагов (рис. 16), а также окно просмотра битов (рис. 19). Значения соответствуют модельному времени, установленному в «навигаторе времени».

Просмотр содержимого дампа памяти осуществляется двумя способами. Первое окно (рис. 18) позволяет изменять настройки окна произвольным образом: изменять систему счисления адреса и данных, устанавливать произвольный размер слова памяти. Второе окно (рис. 19) имеет встроенные настройки.

Реализованы механизмы автоматического расположения окон визуализации в виде горизонтальной и вертикальной «черепицы».

4. Заключение

Использование системы HLCCAD при обучении студентов основам цифровой электроники в значительной степени повышает качество учебного процесса за счёт более активной вовлечённости студентов в процесс, визуализации процесса и результатов работы, интенсификации представления и проверки заданий.